Lattice LC4256V-75FTN256BC: A Comprehensive Technical Overview of the CPLD for Embedded System Design

The Lattice LC4256V-75FTN256BC represents a specific implementation within Lattice Semiconductor's mature but highly reliable ispMACH® 4000V CPLD family. This device continues to be a relevant choice for a wide array of embedded system design tasks, particularly where deterministic timing, high-performance logic integration, and instant-on operation are critical requirements. This overview delves into its architecture, key features, and typical applications within modern electronic systems.

At its core, the LC4256V is a Complex Programmable Logic Device (CPLD) featuring a non-volatile, in-system programmable (ISP) architecture. This non-volatile nature is a key differentiator from FPGAs, as it allows the device to boot instantly upon power application without needing to load a configuration bitstream from an external memory. The device is built upon a macrocell-based architecture, which groups logic resources into blocks. The `4256` in its part number signifies a density of 256 macrocells, providing a substantial amount of programmable logic for implementing state machines, address decoders, complex control logic, and bus interfacing.

The specific part `LC4256V-75FTN256BC` provides detailed information about its capabilities:

`LC4256V`: Denotes the family and macrocell count.

`-75`: Indicates a pin-to-pin propagation delay of 7.5 ns, enabling high-performance operation with system clock speeds well above 100 MHz.

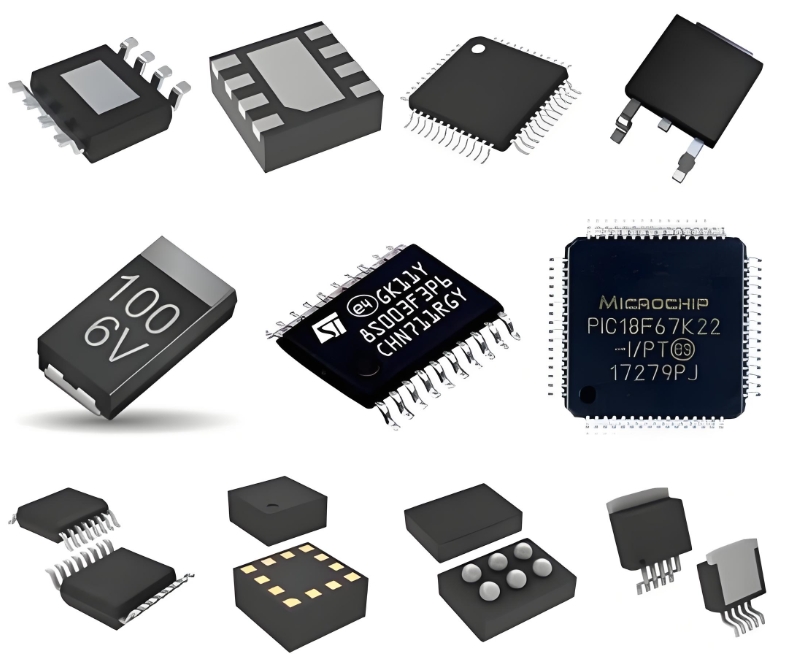

`FTN256`: Specifies the 256-ball Fine-Pitch Ball Grid Array (ftBGA) package. This surface-mount package offers a compact footprint, making it suitable for space-constrained embedded applications.

`B`: Indicates the commercial temperature range (0°C to +90°C TJ).

`C`: The revision of the silicon.

Key technical features that make this CPLD attractive for embedded design include:

High-Density Logic Integration: With 256 macrocells, 128 I/O pins (in the 256-ball package), and over 5,000 PLD gates, it can consolidate numerous discrete logic ICs and simple PLDs into a single chip, reducing board space and component count.

Deterministic Timing: The CPLD's predictable, routable architecture ensures that signal delays are consistent and manageable, which is crucial for interfacing with processors, memory, and other peripherals with strict setup/hold time requirements.

5V Tolerant I/Os: A significant feature for systems with legacy 5V components, the device offers 3.3V operation with 5V tolerance on its I/O pins, simplifying mixed-voltage system design without requiring external level shifters.

In-System Programmability (ISP): The device can be reprogrammed on the board via a standard 4-pin JTAG (IEEE 1149.1) interface. This facilitates rapid design iterations, field upgrades, and prototype debugging without physically removing the chip.

Low Power Consumption: Compared to larger FPGAs, this CPLD family operates with very low standby and dynamic power, an essential factor for power-sensitive applications.

In embedded system design, the LC4256V-75FTN256BC is perfectly suited for a host of "glue logic" and system management functions. Common applications include:

Power-on Sequencing and System Configuration: Controlling the reset and power-up sequence for FPGAs, ASICs, and processors.

Address Decoding and Bus Interfacing: Interfacing between processors and various memory (SRAM, SDRAM, Flash) or peripheral devices with custom chip-select generation.

Data Path Control and Bridging: Implementing interfaces like SPI, I2C, or a simple UART, or bridging between two different bus standards.

State Machine Implementation: Hosting complex control logic for system management that must be active immediately at power-on.

ICGOOODFIND: The Lattice LC4256V-75FTN256BC CPLD is a robust, high-performance, and reliable solution for embedded designers needing to integrate complex logic with predictable timing. Its non-volatile nature, 5V tolerance, and high I/O count make it an excellent choice for system control, interface bridging, and logic consolidation in a wide range of industrial, communications, and computing applications, often serving as the indispensable "glue" that holds a complex electronic system together.

Keywords: CPLD, Non-Volatile, In-System Programmable (ISP), Deterministic Timing, Embedded System Design.